Memórias Cache

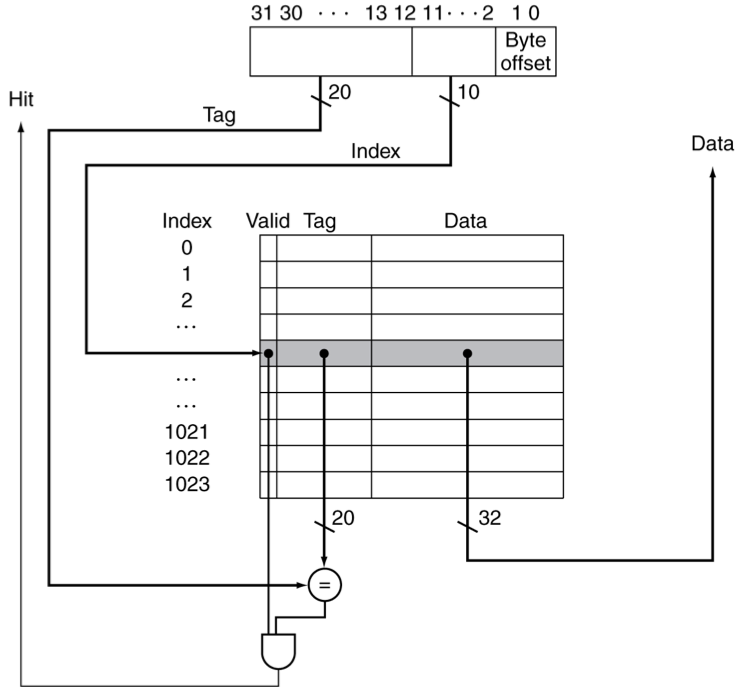

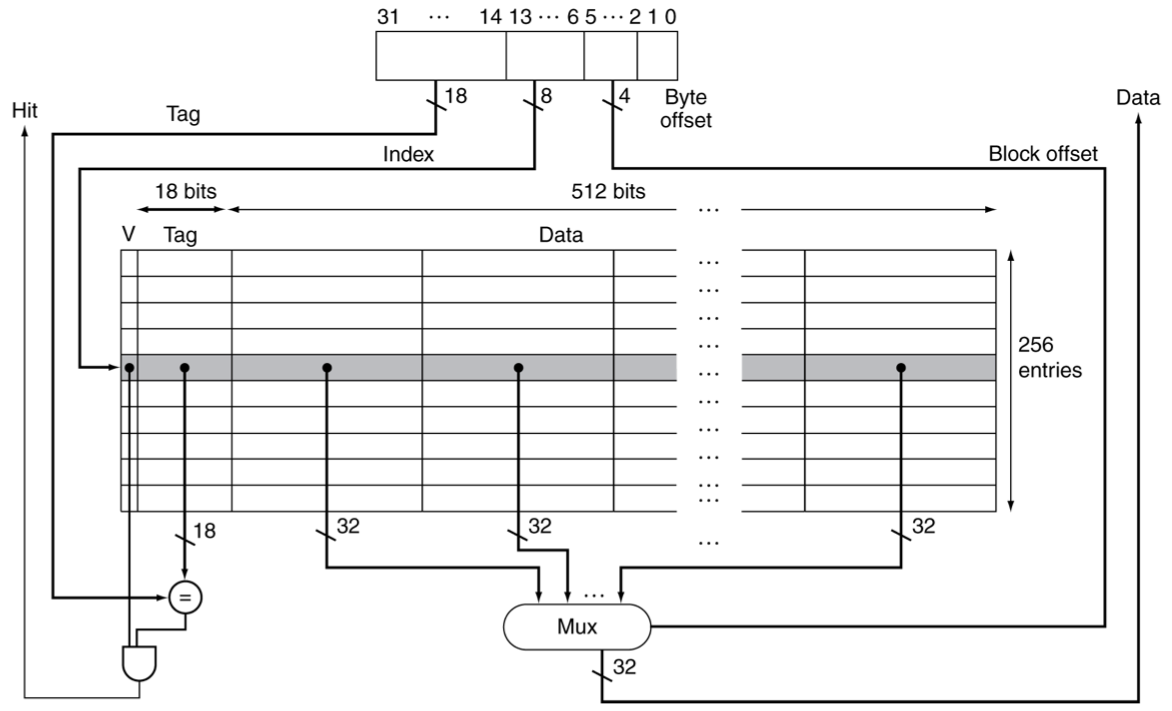

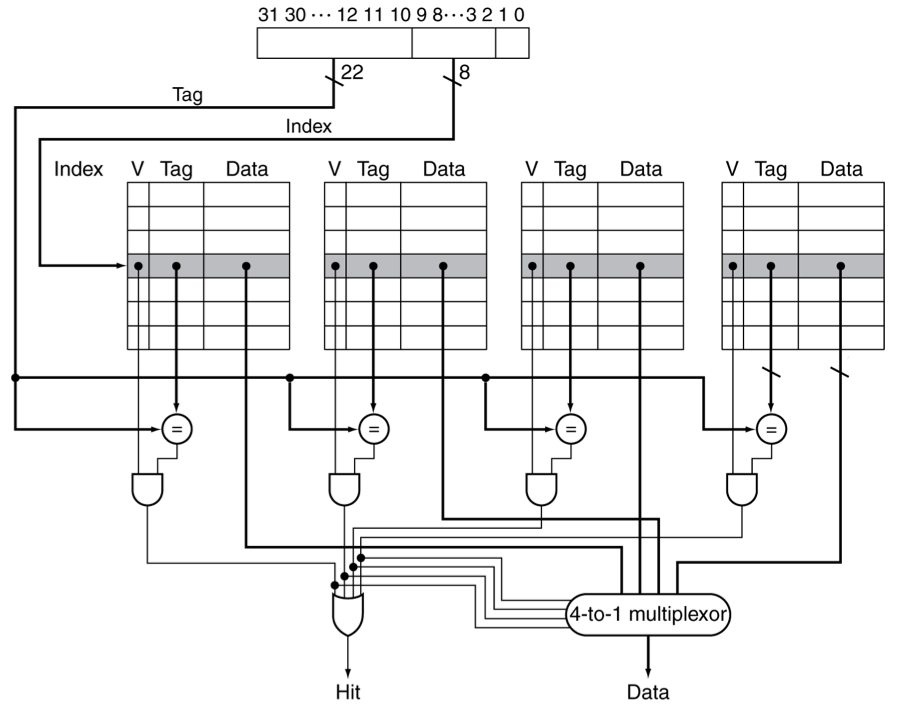

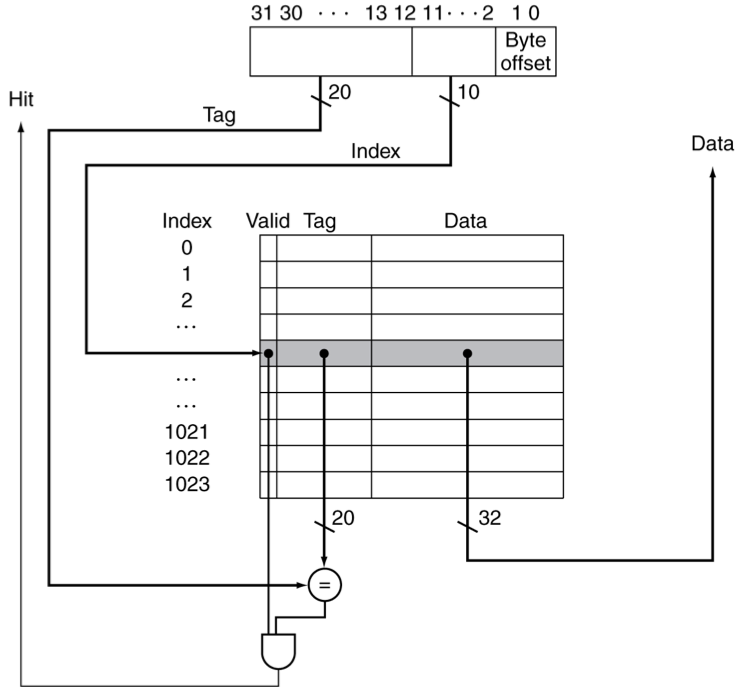

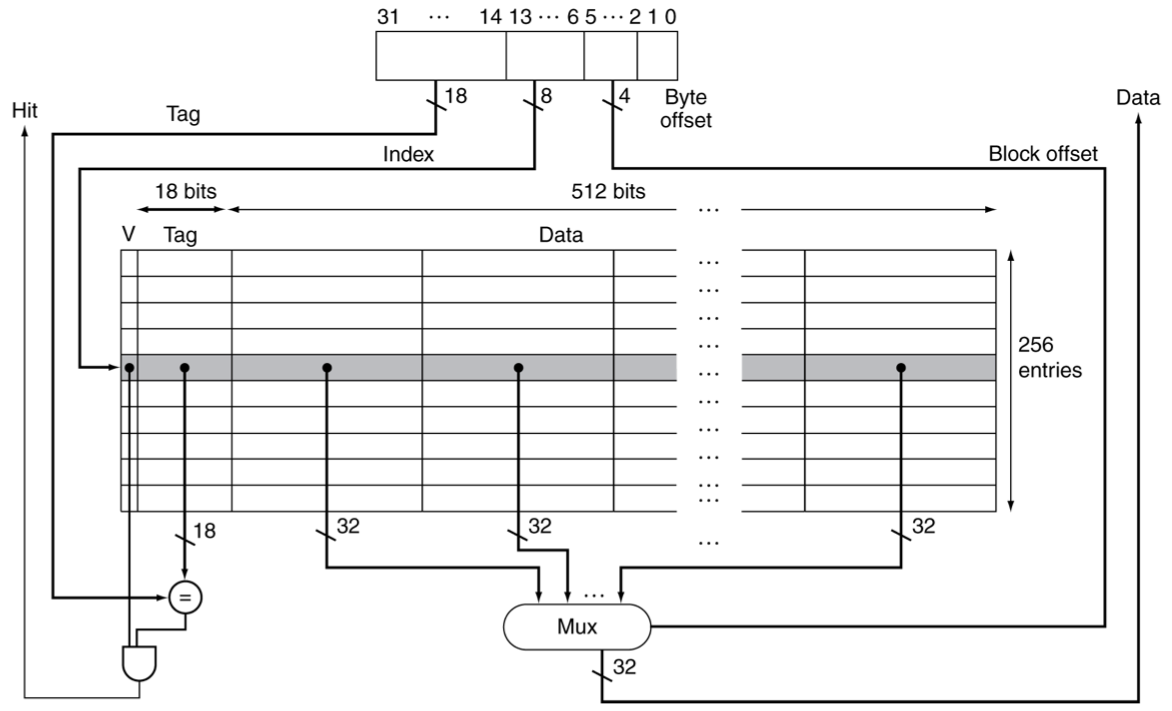

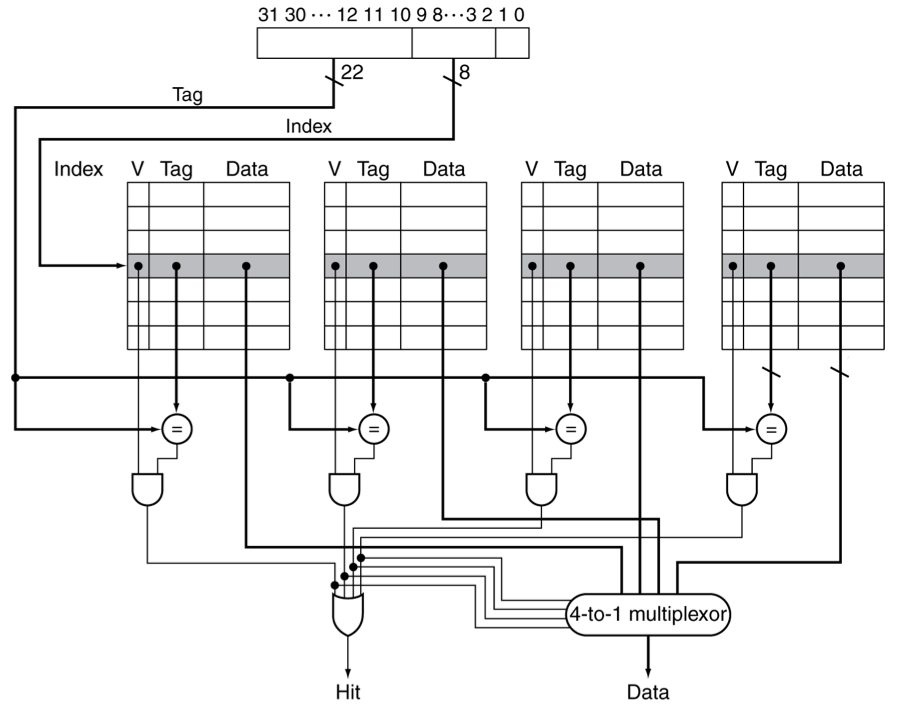

As figuras que se seguem representam diferentes configurações de

memórias cache:

- Cache I

- Cache II

- Cache III

- Para cada memória cache determine a tag e o index associados aos

seguintes endereços:

- 0x0000222c

- 0x00001956

- 0x00004321

- 0x00000037

- Assumindo que a memória principal tem 64 Kbytes, para cada

memória cache indique:

- o tipo de cache

- o número de linhas

- a capacidade de cada linha da cache em bytes

- a capacidade total da cache em bytes

- o número de linhas de cache em que pode ser dividida a memória

- o número de linhas de memória mapeadas na mesma linha da cache

- Assuma agora que a memória principal têm o tamanho máximo

suportado por endereços de 32 bits e para cada memória cache

indique:

- o número de linhas de cache em que pode ser dividida a memória

- o número de linhas de memória mapeadas na mesma linha da cache

- Considere a sequência de referências de acessos a memória que se

segue (endereços em bytes):

12, 720, 172, 8, 764, 352, 760,

56, 724, 176, 744, 1012

- Indique a mesma sequência mas com os endereços em

múltiplos de palavras (words, 4 bytes).

- Dadas 3 caches de mapeamento direto (direct-mapped caches),

C1, C2 e C3, todas com uma capacidade total de 8 palavras,

diga qual a que tem o menor miss rate na sequência acima,

sabendo que a cache C1 usa blocos de 1 palavra, C2 usa

blocos de 2 palavras e C3 usa blocos de 4 palavras.

- Se o miss stall time for de 25 ciclos e C1 tem um tempo de

acesso de 2 ciclos, C2 de 3 ciclos e C3 de 5 ciclos, qual é

a cache com melhor desempenho na sequência acima?